mirror of

https://github.com/Dasharo/twpm-docs.git

synced 2026-03-06 14:53:56 -08:00

Merge pull request #36 from Dasharo/spi

development/verilog_modules.md: add SPI module description

This commit is contained in:

+15

-1

@@ -6,9 +6,23 @@ SPDX-License-Identifier: CC-BY-SA-4.0

|

||||

|

||||

# Changelog

|

||||

|

||||

## 2024-03-14

|

||||

|

||||

* Added testbench outputs to [Verilog modules](../development/verilog_modules/)

|

||||

* Added [SPI module description](../development/verilog_modules/#spi-module)

|

||||

- Reset signal was added to the registers module, required because SPI clock

|

||||

isn't free-running.

|

||||

* Added instructions for [connecting to mainboard through SPI](../tutorials/mainboard-connection/#protectli-vp66xx-spi)

|

||||

* Fixed broken links here and in [Development/Testing](../development/testing/)

|

||||

* Fixed command for running tests in [Development/Testing](../development/testing/)

|

||||

(missing asterisks)

|

||||

* Published

|

||||

[tests results as part of Task 7. Implement SPI TPM protocol](../test-results/2024_01_11_orange_crab_without_create_primary.html)

|

||||

* Updated [FPGA utilisation numbers](../development/verilog_modules/)

|

||||

|

||||

## 2024-01-16

|

||||

|

||||

* Added page about [running tests](../development/testing.md)

|

||||

* Added page about [running tests](../development/testing/)

|

||||

* Published

|

||||

[tests results as part of Task 6. Base tests](../test-results/2024_01_11_orange_crab_without_create_primary.html)

|

||||

* Small changes to

|

||||

|

||||

@@ -47,8 +47,9 @@ Reserved bits are read as 0. They may change in the future.

|

||||

|

||||

* `op_type` is a type of operation expected from MCU. 0 is used as a default

|

||||

value to which this register returns after `complete` signal is acknowledged

|

||||

by FPGA. 0xC is reserved as it may be part of 0xBADFABAC magic value. This

|

||||

register is only valid if `exec` is set.

|

||||

by FPGA, code should treat this value as error because no valid path produces

|

||||

it when requesting interaction from MCU. 0xC is reserved as it may be part of

|

||||

0xBADFABAC magic value. This register is only valid if `exec` is set.

|

||||

|

||||

| op_type | Operation |

|

||||

|--------:|--------------------------------------------|

|

||||

|

||||

@@ -14,24 +14,30 @@ module features. The tests used here are located in the

|

||||

|

||||

## Tests results

|

||||

|

||||

The latest results (as of 11/01/2024) can be found

|

||||

The latest results (as of 14/03/2024) can be found

|

||||

[here](/test-results/2024_03_14_orange_crab_without_create_primary.html). It was

|

||||

run on Protectli VP6670, TwPM was connected through SPI interface. Previous

|

||||

version (running on LPC) is available

|

||||

[here](/test-results/2024_01_11_orange_crab_without_create_primary.html).

|

||||

|

||||

## Hardware setup

|

||||

|

||||

### Hardware list

|

||||

|

||||

* [Protectli VP4670](https://docs.dasharo.com/variants/protectli_vp46xx/overview/)

|

||||

- The TwPM is connected to LPC TPM header on this board, so we can test the

|

||||

TPM features of the TwPM

|

||||

* [Orange Crab](https://github.com/orangecrab-fpga/orangecrab-hardware)

|

||||

- The TwPM is implemented on this board

|

||||

* One of:

|

||||

- [Protectli VP4670](https://docs.dasharo.com/variants/protectli_vp46xx/overview/),

|

||||

the TwPM is connected to LPC TPM header on this board

|

||||

- [Protectli VP6670](https://eu.protectli.com/product/vp6670/),

|

||||

the TwPM is connected to SPI TPM header on this board

|

||||

|

||||

### Connection to the platform

|

||||

|

||||

Follow the [mainboard connection tutorial](/tutorials/mainboard-connection/).

|

||||

Make sure that LCLK and LAD lines aren't directly next to each other (e.g.

|

||||

separate those with GND), otherwise inter-signal noise would cause bad reads.

|

||||

In case of LPC, make sure that LCLK and LAD lines aren't directly next to each

|

||||

other (e.g. separate those with GND), otherwise inter-signal noise would cause

|

||||

bad reads. No such interference was observed for SPI.

|

||||

|

||||

|

||||

|

||||

@@ -61,8 +67,9 @@ the USB-UART converter must also be connected.

|

||||

> [this issue](https://github.com/Dasharo/TwPM_toplevel/issues/23).

|

||||

> Replace `$DEVICE_IP` with the IP address of your device, where TwPM is

|

||||

> connected. It is assumed running Ubuntu 22.04 OS with OpenSSH server enabled

|

||||

> via password authentication.

|

||||

> via password authentication. For this test suite, both VP4670 and VP6670 may

|

||||

> use `protectli-vp4670` configuration.

|

||||

|

||||

```bash

|

||||

robot -L TRACE -v device_ip:$DEVICE_IP -v config:protectli-vp4670 -v snipeit:no -t "TPMCMD00[0-469]" -t "TPMCMD010" dasharo-security/tpm2-commands.robot

|

||||

robot -L TRACE -v device_ip:$DEVICE_IP -v config:protectli-vp4670 -v snipeit:no -t "TPMCMD00[0-469]*" -t "TPMCMD010*" dasharo-security/tpm2-commands.robot

|

||||

```

|

||||

|

||||

@@ -19,38 +19,72 @@ a guess about signal function based only on its name, which in some cases gives

|

||||

wrong results. Such cases are mentioned in the signal descriptions under the

|

||||

diagrams.

|

||||

|

||||

Current FPGA utilization:

|

||||

Current FPGA utilization for LPC:

|

||||

|

||||

```text

|

||||

Info: Device utilisation:

|

||||

Info: TRELLIS_IO: 65/ 197 32%

|

||||

Info: DCCA: 5/ 56 8%

|

||||

Info: DP16KD: 5/ 56 8%

|

||||

Info: MULT18X18D: 1/ 28 3%

|

||||

Info: ALU54B: 0/ 14 0%

|

||||

Info: EHXPLLL: 1/ 2 50%

|

||||

Info: EXTREFB: 0/ 1 0%

|

||||

Info: DCUA: 0/ 1 0%

|

||||

Info: PCSCLKDIV: 0/ 2 0%

|

||||

Info: IOLOGIC: 44/ 128 34%

|

||||

Info: SIOLOGIC: 0/ 69 0%

|

||||

Info: GSR: 0/ 1 0%

|

||||

Info: JTAGG: 0/ 1 0%

|

||||

Info: OSCG: 0/ 1 0%

|

||||

Info: SEDGA: 0/ 1 0%

|

||||

Info: DTR: 0/ 1 0%

|

||||

Info: USRMCLK: 1/ 1 100%

|

||||

Info: CLKDIVF: 1/ 4 25%

|

||||

Info: ECLKSYNCB: 1/ 10 10%

|

||||

Info: DLLDELD: 0/ 8 0%

|

||||

Info: DDRDLL: 1/ 4 25%

|

||||

Info: DQSBUFM: 2/ 8 25%

|

||||

Info: TRELLIS_ECLKBUF: 3/ 8 37%

|

||||

Info: ECLKBRIDGECS: 1/ 2 50%

|

||||

Info: DCSC: 0/ 2 0%

|

||||

Info: TRELLIS_FF: 5081/24288 20%

|

||||

Info: TRELLIS_COMB: 12350/24288 50%

|

||||

Info: TRELLIS_RAMW: 121/ 3036 3%

|

||||

Info: TRELLIS_IO: 65/ 197 32%

|

||||

Info: DCCA: 5/ 56 8%

|

||||

Info: DP16KD: 5/ 56 8%

|

||||

Info: MULT18X18D: 1/ 28 3%

|

||||

Info: ALU54B: 0/ 14 0%

|

||||

Info: EHXPLLL: 1/ 2 50%

|

||||

Info: EXTREFB: 0/ 1 0%

|

||||

Info: DCUA: 0/ 1 0%

|

||||

Info: PCSCLKDIV: 0/ 2 0%

|

||||

Info: IOLOGIC: 44/ 128 34%

|

||||

Info: SIOLOGIC: 0/ 69 0%

|

||||

Info: GSR: 0/ 1 0%

|

||||

Info: JTAGG: 0/ 1 0%

|

||||

Info: OSCG: 0/ 1 0%

|

||||

Info: SEDGA: 0/ 1 0%

|

||||

Info: DTR: 0/ 1 0%

|

||||

Info: USRMCLK: 1/ 1 100%

|

||||

Info: CLKDIVF: 1/ 4 25%

|

||||

Info: ECLKSYNCB: 1/ 10 10%

|

||||

Info: DLLDELD: 0/ 8 0%

|

||||

Info: DDRDLL: 1/ 4 25%

|

||||

Info: DQSBUFM: 2/ 8 25%

|

||||

Info: TRELLIS_ECLKBUF: 3/ 8 37%

|

||||

Info: ECLKBRIDGECS: 1/ 2 50%

|

||||

Info: DCSC: 0/ 2 0%

|

||||

Info: TRELLIS_FF: 5049/24288 20%

|

||||

Info: TRELLIS_COMB: 12639/24288 52%

|

||||

Info: TRELLIS_RAMW: 121/ 3036 3%

|

||||

```

|

||||

|

||||

Current FPGA utilization for SPI:

|

||||

|

||||

```text

|

||||

Info: Device utilisation:

|

||||

Info: TRELLIS_IO: 62/ 197 31%

|

||||

Info: DCCA: 6/ 56 10%

|

||||

Info: DP16KD: 5/ 56 8%

|

||||

Info: MULT18X18D: 0/ 28 0%

|

||||

Info: ALU54B: 0/ 14 0%

|

||||

Info: EHXPLLL: 1/ 2 50%

|

||||

Info: EXTREFB: 0/ 1 0%

|

||||

Info: DCUA: 0/ 1 0%

|

||||

Info: PCSCLKDIV: 0/ 2 0%

|

||||

Info: IOLOGIC: 44/ 128 34%

|

||||

Info: SIOLOGIC: 0/ 69 0%

|

||||

Info: GSR: 0/ 1 0%

|

||||

Info: JTAGG: 0/ 1 0%

|

||||

Info: OSCG: 0/ 1 0%

|

||||

Info: SEDGA: 0/ 1 0%

|

||||

Info: DTR: 0/ 1 0%

|

||||

Info: USRMCLK: 1/ 1 100%

|

||||

Info: CLKDIVF: 1/ 4 25%

|

||||

Info: ECLKSYNCB: 1/ 10 10%

|

||||

Info: DLLDELD: 0/ 8 0%

|

||||

Info: DDRDLL: 1/ 4 25%

|

||||

Info: DQSBUFM: 2/ 8 25%

|

||||

Info: TRELLIS_ECLKBUF: 3/ 8 37%

|

||||

Info: ECLKBRIDGECS: 1/ 2 50%

|

||||

Info: DCSC: 0/ 2 0%

|

||||

Info: TRELLIS_FF: 5025/24288 20%

|

||||

Info: TRELLIS_COMB: 12175/24288 50%

|

||||

Info: TRELLIS_RAMW: 121/ 3036 3%

|

||||

```

|

||||

|

||||

## Top level

|

||||

@@ -82,9 +116,15 @@ External ports:

|

||||

marked as negated on the diagram due to how Symbolator detects such signals,

|

||||

i.e. its name doesn't end with either `_n` or `_b`).

|

||||

- `uart_rxd_i`, `uart_txd_o`: UART running at 115200n8.

|

||||

- LPC signals: those are to be connected to the mainboard, see

|

||||

[Connecting TwPM to mainboard](/tutorials/mainboard-connection/).

|

||||

- SPI signals: connected to onboard SPI flash. Note that there is no clock

|

||||

- LPC interface: those are to be connected to the mainboard, see

|

||||

[Connecting TwPM to mainboard](/tutorials/mainboard-connection/). Note that

|

||||

only one of LPC or SPI interface is present at any given time, depending on

|

||||

build configuration.

|

||||

- SPI interface: those are to be connected to the mainboard, see

|

||||

[Connecting TwPM to mainboard](/tutorials/mainboard-connection/). Note that

|

||||

only one of LPC or SPI interface is present at any given time, depending on

|

||||

build configuration.

|

||||

- SPI flash signals: connected to onboard SPI flash. Note that there is no clock

|

||||

signal on the diagram, a hardware macro must be used instead of defining it as

|

||||

a port.

|

||||

- DDR3 interface: signals to and from onboard DRAM, connected directly to

|

||||

@@ -158,6 +198,50 @@ List of ports:

|

||||

|

||||

Source code: [Dasharo/verilog-lpc-module](https://github.com/Dasharo/verilog-lpc-module)

|

||||

|

||||

Testbench results:

|

||||

|

||||

```text

|

||||

VCD info: dumpfile lpc_periph_tb.vcd opened for output.

|

||||

Performing TPM write w/o delay

|

||||

Performing TPM write with delay

|

||||

Performing TPM read with delay

|

||||

Performing TPM read w/o delay

|

||||

Testing reset behaviour - TPM write w/o delay

|

||||

Testing reset behaviour - TPM read w/o delay

|

||||

Testing reset behaviour - TPM write with delay

|

||||

Testing reset behaviour - TPM read with delay

|

||||

Testing non-TPM transactions

|

||||

Testing extended LFRAME# timings - write

|

||||

Testing extended LFRAME# timings - read

|

||||

Testing abort mechanism - write

|

||||

Testing abort mechanism - read

|

||||

Testing interrupts - Continuous mode:

|

||||

no interrupt reported when not requested?

|

||||

proper IRQ reported?

|

||||

IRQ number latched at start frame?

|

||||

IRQ keeps being sent while active?

|

||||

IRQ stops being sent when no longer active?

|

||||

recovery and turn-around phases executed when int is deactivated?

|

||||

IRQs reported with idle clock cycles before stop frame?

|

||||

IRQs reported with idle clock cycles after stop frame?

|

||||

IRQs reported with longer start pulse width?

|

||||

Testing interrupts - switching between modes:

|

||||

peripheral doesn't initialize SERIRQ cycle in Quiet mode when not needed?

|

||||

peripheral initializes SERIRQ cycle when IRQ needed in Quiet mode?

|

||||

reset switches peripheral to Continuous mode?

|

||||

Testing interrupts - Quiet mode:

|

||||

proper IRQ reported?

|

||||

IRQ number latched at start frame?

|

||||

IRQ keeps being sent while active?

|

||||

IRQ stops being sent when no longer active?

|

||||

recovery and turn-around phases executed when int is deactivated?

|

||||

IRQs reported with idle clock cycles before stop frame?

|

||||

peripheral keeps working after spurious interrupt?

|

||||

IRQs reported with longer start pulse width?

|

||||

Testing interrupts - IRQ stops being reported on reset

|

||||

lpc_periph_tb.v:1344: $stop called at 518601000 (1ps)

|

||||

```

|

||||

|

||||

This module is responsible for managing LPC communication. It responds only to

|

||||

TPM cycles, other cycle types are ignored. SERIRQ (both continuous and quiet

|

||||

mode), cycle aborts and LPC resets are implemented.

|

||||

@@ -211,36 +295,113 @@ Ports for signals to/from data provider:

|

||||

that, in quiet mode this signal initializes SERIRQ cycle. Data provider should

|

||||

drive this signal as long as reason for interrupt is valid.

|

||||

|

||||

## SPI module

|

||||

|

||||

Source code: [Dasharo/verilog-spi-module](https://github.com/Dasharo/verilog-spi-module)

|

||||

|

||||

Testbench results:

|

||||

|

||||

```text

|

||||

VCD info: dumpfile spi_periph_tb.vcd opened for output.

|

||||

Performing TPM write w/o delay

|

||||

Performing TPM write with delay

|

||||

Performing TPM read with delay

|

||||

Performing TPM read w/o delay

|

||||

Testing transfers with scattered clock between bytes

|

||||

Testing over-sized transfers

|

||||

Testing non-TPM addresses

|

||||

Testing crossing registers boundary

|

||||

spi_periph_tb.v:349: $stop called at 86540000 (1ps)

|

||||

```

|

||||

|

||||

This module is responsible for managing SPI communication with PC. It only

|

||||

supports SPI protocol as described in TPM specification.

|

||||

|

||||

|

||||

|

||||

Ports for SPI interface:

|

||||

|

||||

- `clk_i`: SPI clock.

|

||||

- `cs_n`: Chip select (active low).

|

||||

- `mosi`: SPI Main Out Sub In.

|

||||

- `miso`: SPI Main In Sub Out, slow pull-up on host side.

|

||||

|

||||

Ports for signals to/from data provider:

|

||||

|

||||

- `addr_o`: 16-bit address of TPM register.

|

||||

- `data_i`, `data_o`: data received from or sent to TPM registers module.

|

||||

- `data_wr`: signal to data provider that `addr_o` and `data_o` have valid data

|

||||

and write is requested.

|

||||

- `wr_done`: signal from data provider that `data_o` has been read. This signal

|

||||

isn't used by SPI module because it would most likely arrive when the clock is

|

||||

no longer running. Contrary to the LPC, SPI clock runs only during the

|

||||

transmission.

|

||||

- `data_req`: signal to data provider that data is requested.

|

||||

- `data_rd`: signal from data provider that `data_i` has valid data for reading.

|

||||

This signal should be driven in response to `data_req`.

|

||||

|

||||

Note that there are no signals responsible for interrupts. SPI uses PIRQ, which

|

||||

doesn't require any additional logic, so `interrupt` signal from TPM registers

|

||||

module is used to drive it directly in the top level module.

|

||||

|

||||

## TPM registers module

|

||||

|

||||

Source code: [Dasharo/verilog-tpm-fifo-registers](https://github.com/Dasharo/verilog-tpm-fifo-registers)

|

||||

|

||||

Testbench results:

|

||||

|

||||

```text

|

||||

VCD info: dumpfile regs_tb.vcd opened for output.

|

||||

Testing simple register reads without delay

|

||||

Testing simple register reads with delay

|

||||

Checking register values against expected.txt

|

||||

Checking if RO registers are writable

|

||||

Testing mechanisms for changing locality

|

||||

Testing mechanisms for seizing locality

|

||||

Testing TPM_INT_VECTOR write without delay - proper locality

|

||||

Testing TPM_INT_VECTOR write with delay - proper locality

|

||||

Testing TPM_INT_VECTOR write without delay - wrong locality

|

||||

Testing TPM_INT_VECTOR write with delay - wrong locality

|

||||

Testing TPM_INT_VECTOR write without delay - no locality

|

||||

Testing TPM_INT_VECTOR write with delay - no locality

|

||||

Testing command/response exchange and TPM state machine - basic

|

||||

Testing command/response exchange and TPM state machine - advanced

|

||||

regs_tb.v:1075: $stop called at 2023220000 (1ps)

|

||||

```

|

||||

|

||||

This module implements TPM register space. It also handles locality transitions,

|

||||

TPM interrupt generation and command finite state machine. Register values are

|

||||

reported accordingly to the current state. Registers not defined by PC Client

|

||||

specification return 0xFF on reads, and writes are dropped.

|

||||

|

||||

The module is located between host interface module (LPC or, in the future, SPI)

|

||||

and memory buffer for TPM commands and responses. It also exposes hardware

|

||||

interface that is translated by top module into software interface for TPM stack

|

||||

running on NEORV32 processor.

|

||||

The module is located between host interface module (LPC or SPI) and memory

|

||||

buffer for TPM commands and responses. It also exposes hardware interface that

|

||||

is translated by top module into software interface for TPM stack running on

|

||||

NEORV32 processor.

|

||||

|

||||

|

||||

|

||||

Ports for signals to/from LPC module:

|

||||

Ports for signals to/from LPC or SPI module:

|

||||

|

||||

- `clk_i`: LPC clock is used for this module to allow for synchronous

|

||||

communication with LPC module. Because of that, all registers' values are

|

||||

available in one clock cycle and no wait states have to be inserted.

|

||||

- `clk_i`: LPC/SPI clock is used for this module to allow for synchronous

|

||||

communication with LPC/SPI module. Because of that, all registers' values are

|

||||

available in one clock cycle and no wait states (LPC) or exactly one wait

|

||||

state (SPI) has to be inserted. For LPC,the clock is free-running, but for SPI

|

||||

it is enabled only during the communication.

|

||||

- `reset`: reset signal, required to reset registers to their initial values,

|

||||

active low.

|

||||

- `addr_i`: 16-bit address of register to access.

|

||||

- `data_i`: 8-bit data from LPC module.

|

||||

- `data_o`: 8-bit data to LPC module.

|

||||

- `data_i`: 8-bit data from LPC/SPI module.

|

||||

- `data_o`: 8-bit data to LPC/SPI module.

|

||||

- `data_wr`, `wr_done`, `data_req`, `data_rd`: 4 signals coordinating

|

||||

communication over `data_i` and `data_o`. Their functions can be found in the

|

||||

[LPC module description](#lpc-module) above.

|

||||

[LPC module description](#lpc-module) or [SPI module description](#spi-module)

|

||||

above.

|

||||

- `irq_num`, `interrupt`: configuration and request of interrupts sent to host,

|

||||

see [LPC module description](#lpc-module) for details. Note that these are not

|

||||

interrupts sent towards NEORV32.

|

||||

see [LPC module description](#lpc-module) for details. In case of SPI,

|

||||

`interrupt` is negated and routed directly to I/O pin in top level and

|

||||

`irq_num` is not used. Note that these are not interrupts sent towards

|

||||

NEORV32.

|

||||

|

||||

Ports for signals for MCU interface:

|

||||

|

||||

@@ -284,5 +445,5 @@ Ports:

|

||||

|

||||

- `A`: address, counted in 32-bit words.

|

||||

- `WD`, `RD`: input and output data, respectively.

|

||||

- `Clk`: input clock, arbitrated by top level between LPC and system clocks.

|

||||

- `Clk`: input clock, arbitrated by top level between LPC/SPI and system clocks.

|

||||

- `WEN`: write enable for each byte of `WD`.

|

||||

|

||||

Binary file not shown.

|

After Width: | Height: | Size: 2.6 KiB |

@@ -0,0 +1,3 @@

|

||||

SPDX-FileCopyrightText: 2024 3mdeb <contact@3mdeb.com>

|

||||

|

||||

SPDX-License-Identifier: CC-BY-SA-4.0

|

||||

@@ -3,7 +3,7 @@

|

||||

<svg xmlns="http://www.w3.org/2000/svg"

|

||||

xmlns:xlink="http://www.w3.org/1999/xlink"

|

||||

xml:space="preserve"

|

||||

width="678" height="390" viewBox="-108 -20 678.0 390.0" version="1.1">

|

||||

width="678" height="410" viewBox="-108 -20 678.0 410.0" version="1.1">

|

||||

<style type="text/css">

|

||||

<![CDATA[

|

||||

.fnt1 {fill:#000000;

|

||||

@@ -33,7 +33,7 @@ width="678" height="390" viewBox="-108 -20 678.0 390.0" version="1.1">

|

||||

</g>

|

||||

<rect x="1.0" y="-14.0" width="318.0" height="28.0" stroke="#646464" fill="none" stroke-width="3"/>

|

||||

<g transform="translate(0,38.0)">

|

||||

<rect x="0" y="-15.0" width="320" height="127.0" stroke="#000000" fill="#C5DBFC" stroke-width="1"/>

|

||||

<rect x="0" y="-15.0" width="320" height="147.0" stroke="#000000" fill="#C5DBFC" stroke-width="1"/>

|

||||

<text class="fnt2" x="160.0" y="0" text-anchor="middle" dy="2.5">LPC/SPI module interface</text>

|

||||

<g transform="translate(0,17)">

|

||||

<line x1="-20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="1" marker-end="url(#clock)"/>

|

||||

@@ -41,21 +41,26 @@ width="678" height="390" viewBox="-108 -20 678.0 390.0" version="1.1">

|

||||

<text class="fnt1" x="-30" y="0" text-anchor="end" dy="3.5" style="fill:#969696">wire</text>

|

||||

</g>

|

||||

<g transform="translate(0,37)">

|

||||

<line x1="-20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="1"/>

|

||||

<text class="fnt1" x="10" y="0" text-anchor="normal" dy="3.5">reset</text>

|

||||

<text class="fnt1" x="-30" y="0" text-anchor="end" dy="3.5" style="fill:#969696">wire</text>

|

||||

</g>

|

||||

<g transform="translate(0,57)">

|

||||

<line x1="-20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="3"/>

|

||||

<text class="fnt1" x="10" y="0" text-anchor="normal" dy="3.5">data_i</text>

|

||||

<text class="fnt1" x="-30" y="0" text-anchor="end" dy="3.5" style="fill:#969696">wire <tspan fill="#039BE5">[7:0]</tspan></text>

|

||||

</g>

|

||||

<g transform="translate(0,57)">

|

||||

<g transform="translate(0,77)">

|

||||

<line x1="-20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="3"/>

|

||||

<text class="fnt1" x="10" y="0" text-anchor="normal" dy="3.5">addr_i</text>

|

||||

<text class="fnt1" x="-30" y="0" text-anchor="end" dy="3.5" style="fill:#969696">wire <tspan fill="#039BE5">[15:0]</tspan></text>

|

||||

</g>

|

||||

<g transform="translate(0,77)">

|

||||

<g transform="translate(0,97)">

|

||||

<line x1="-20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="1"/>

|

||||

<text class="fnt1" x="10" y="0" text-anchor="normal" dy="3.5">data_wr</text>

|

||||

<text class="fnt1" x="-30" y="0" text-anchor="end" dy="3.5" style="fill:#969696">wire</text>

|

||||

</g>

|

||||

<g transform="translate(0,97)">

|

||||

<g transform="translate(0,117)">

|

||||

<line x1="-20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="1"/>

|

||||

<text class="fnt1" x="10" y="0" text-anchor="normal" dy="3.5">data_req</text>

|

||||

<text class="fnt1" x="-30" y="0" text-anchor="end" dy="3.5" style="fill:#969696">wire</text>

|

||||

@@ -86,7 +91,7 @@ width="678" height="390" viewBox="-108 -20 678.0 390.0" version="1.1">

|

||||

<text class="fnt1" x="30" y="0" text-anchor="normal" dy="3.5" style="fill:#969696">reg</text>

|

||||

</g>

|

||||

</g>

|

||||

<g transform="translate(0,165.0)">

|

||||

<g transform="translate(0,185.0)">

|

||||

<rect x="0" y="-15.0" width="320" height="127.0" stroke="#000000" fill="#E7FDBA" stroke-width="1"/>

|

||||

<text class="fnt2" x="160.0" y="0" text-anchor="middle" dy="2.5">MCU data and interrupts interface</text>

|

||||

<g transform="translate(0,17)">

|

||||

@@ -120,7 +125,7 @@ width="678" height="390" viewBox="-108 -20 678.0 390.0" version="1.1">

|

||||

<text class="fnt1" x="30" y="0" text-anchor="normal" dy="3.5" style="fill:#969696">reg</text>

|

||||

</g>

|

||||

</g>

|

||||

<g transform="translate(0,292.0)">

|

||||

<g transform="translate(0,312.0)">

|

||||

<rect x="0" y="-15.0" width="320" height="87.0" stroke="#000000" fill="#FFAFFD" stroke-width="1"/>

|

||||

<text class="fnt2" x="160.0" y="0" text-anchor="middle" dy="2.5">RAM interface</text>

|

||||

<g transform="translate(0,17)">

|

||||

@@ -144,5 +149,5 @@ width="678" height="390" viewBox="-108 -20 678.0 390.0" version="1.1">

|

||||

<text class="fnt1" x="30" y="0" text-anchor="normal" dy="3.5" style="fill:#969696">reg</text>

|

||||

</g>

|

||||

</g>

|

||||

<rect x="1.0" y="24.0" width="318.0" height="339.0" stroke="#000000" fill="none" stroke-width="3"/>

|

||||

<rect x="1.0" y="24.0" width="318.0" height="359.0" stroke="#000000" fill="none" stroke-width="3"/>

|

||||

</svg>

|

||||

|

||||

|

Before Width: | Height: | Size: 8.4 KiB After Width: | Height: | Size: 8.7 KiB |

@@ -0,0 +1,95 @@

|

||||

<?xml version="1.0" encoding="UTF-8" standalone="no"?>

|

||||

<!-- Created by Symbolator http://kevinpt.github.io/symbolator -->

|

||||

<svg xmlns="http://www.w3.org/2000/svg"

|

||||

xmlns:xlink="http://www.w3.org/1999/xlink"

|

||||

xml:space="preserve"

|

||||

width="460" height="205" viewBox="-99 -20 460.0 205.0" version="1.1">

|

||||

<style type="text/css">

|

||||

<![CDATA[

|

||||

.fnt1 {fill:#000000;

|

||||

font-family:Times; font-size:12pt; font-weight:normal; font-style:italic;}

|

||||

.fnt2 {fill:#000000;

|

||||

font-family:Helvetica; font-size:12pt; font-weight:normal; font-style:normal;}

|

||||

.label {fill:#000;

|

||||

text-anchor:middle;

|

||||

font-size:16pt; font-weight:bold; font-family:Sans;}

|

||||

.link {fill: #0D47A1;}

|

||||

.link:hover {fill: #0D47A1; text-decoration:underline;}

|

||||

.link:visited {fill: #4A148C;}

|

||||

]]>

|

||||

</style>

|

||||

<defs>

|

||||

<marker id="clock" markerWidth="8.0" markerHeight="15.0" viewBox="0 0 8.0 15.0" refX="0.5" refY="7.5" orient="auto" markerUnits="userSpaceOnUse">

|

||||

<g transform="translate(0.5,7.5)"><path d="M 0 -7 L 0 7 L 7 0 z" stroke="#000000" fill="#FFFFFF" stroke-width="1"/>

|

||||

</g>

|

||||

</marker>

|

||||

<marker id="bubble" markerWidth="7.0" markerHeight="7.0" viewBox="0 0 7.0 7.0" refX="3.5" refY="3.5" orient="auto" markerUnits="userSpaceOnUse">

|

||||

<g transform="translate(3.5,3.5)"><ellipse cx="0.0" cy="0.0" rx="3.0" ry="3.0" stroke="#000000" fill="#FFFFFF" stroke-width="1"/>

|

||||

</g>

|

||||

</marker>

|

||||

</defs>

|

||||

<rect x="-99" y="-20" width="100%" height="100%" fill="white"/><g transform="translate(0,0)">

|

||||

<rect x="0" y="-15.0" width="260" height="87.0" stroke="#000000" fill="#C5DBFC" stroke-width="1"/>

|

||||

<text class="fnt1" x="130.0" y="0" text-anchor="middle" dy="2.5">SPI interface</text>

|

||||

<g transform="translate(0,17)">

|

||||

<line x1="-20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="1" marker-end="url(#clock)"/>

|

||||

<text class="fnt2" x="10" y="0" text-anchor="normal" dy="3.5">clk_i</text>

|

||||

<text class="fnt2" x="-30" y="0" text-anchor="end" dy="3.5" style="fill:#969696">wire</text>

|

||||

</g>

|

||||

<g transform="translate(0,37)">

|

||||

<line x1="-20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="1"/>

|

||||

<text class="fnt2" x="10" y="0" text-anchor="normal" dy="3.5">mosi</text>

|

||||

<text class="fnt2" x="-30" y="0" text-anchor="end" dy="3.5" style="fill:#969696">wire</text>

|

||||

</g>

|

||||

<g transform="translate(0,57)">

|

||||

<line x1="-20" y1="0" x2="-3.5" y2="0.0" stroke="#000000" fill="none" stroke-width="1" marker-end="url(#bubble)"/>

|

||||

<text class="fnt2" x="10" y="0" text-anchor="normal" dy="3.5">cs_n</text>

|

||||

<text class="fnt2" x="-30" y="0" text-anchor="end" dy="3.5" style="fill:#969696">wire</text>

|

||||

</g>

|

||||

<g transform="translate(260,17)">

|

||||

<line x1="20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="1"/>

|

||||

<text class="fnt2" x="-10" y="0" text-anchor="end" dy="3.5">miso</text>

|

||||

<text class="fnt2" x="30" y="0" text-anchor="normal" dy="3.5" style="fill:#969696">wire</text>

|

||||

</g>

|

||||

</g>

|

||||

<g transform="translate(0,87.0)">

|

||||

<rect x="0" y="-15.0" width="260" height="107.0" stroke="#000000" fill="#E7FDBA" stroke-width="1"/>

|

||||

<text class="fnt1" x="130.0" y="0" text-anchor="middle" dy="2.5">Interface to data provider</text>

|

||||

<g transform="translate(0,17)">

|

||||

<line x1="-20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="3"/>

|

||||

<text class="fnt2" x="10" y="0" text-anchor="normal" dy="3.5">data_i</text>

|

||||

<text class="fnt2" x="-30" y="0" text-anchor="end" dy="3.5" style="fill:#969696">wire <tspan fill="#039BE5">[7:0]</tspan></text>

|

||||

</g>

|

||||

<g transform="translate(0,37)">

|

||||

<line x1="-20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="1"/>

|

||||

<text class="fnt2" x="10" y="0" text-anchor="normal" dy="3.5">wr_done</text>

|

||||

<text class="fnt2" x="-30" y="0" text-anchor="end" dy="3.5" style="fill:#969696">wire</text>

|

||||

</g>

|

||||

<g transform="translate(0,57)">

|

||||

<line x1="-20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="1"/>

|

||||

<text class="fnt2" x="10" y="0" text-anchor="normal" dy="3.5">data_rd</text>

|

||||

<text class="fnt2" x="-30" y="0" text-anchor="end" dy="3.5" style="fill:#969696">wire</text>

|

||||

</g>

|

||||

<g transform="translate(260,17)">

|

||||

<line x1="20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="3"/>

|

||||

<text class="fnt2" x="-10" y="0" text-anchor="end" dy="3.5">data_o</text>

|

||||

<text class="fnt2" x="30" y="0" text-anchor="normal" dy="3.5" style="fill:#969696">reg <tspan fill="#039BE5">[7:0]</tspan></text>

|

||||

</g>

|

||||

<g transform="translate(260,37)">

|

||||

<line x1="20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="3"/>

|

||||

<text class="fnt2" x="-10" y="0" text-anchor="end" dy="3.5">addr_o</text>

|

||||

<text class="fnt2" x="30" y="0" text-anchor="normal" dy="3.5" style="fill:#969696">reg <tspan fill="#039BE5">[15:0]</tspan></text>

|

||||

</g>

|

||||

<g transform="translate(260,57)">

|

||||

<line x1="20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="1"/>

|

||||

<text class="fnt2" x="-10" y="0" text-anchor="end" dy="3.5">data_wr</text>

|

||||

<text class="fnt2" x="30" y="0" text-anchor="normal" dy="3.5" style="fill:#969696">reg</text>

|

||||

</g>

|

||||

<g transform="translate(260,77)">

|

||||

<line x1="20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="1"/>

|

||||

<text class="fnt2" x="-10" y="0" text-anchor="end" dy="3.5">data_req</text>

|

||||

<text class="fnt2" x="30" y="0" text-anchor="normal" dy="3.5" style="fill:#969696">reg</text>

|

||||

</g>

|

||||

</g>

|

||||

<rect x="1.0" y="-14.0" width="258.0" height="192.0" stroke="#000000" fill="none" stroke-width="3"/>

|

||||

</svg>

|

||||

|

After Width: | Height: | Size: 5.2 KiB |

@@ -3,7 +3,7 @@

|

||||

<svg xmlns="http://www.w3.org/2000/svg"

|

||||

xmlns:xlink="http://www.w3.org/1999/xlink"

|

||||

xml:space="preserve"

|

||||

width="456" height="931" viewBox="-108 -20 456.0 931.0" version="1.1">

|

||||

width="496" height="1018" viewBox="-108 -20 496.0 1018.0" version="1.1">

|

||||

<style type="text/css">

|

||||

<![CDATA[

|

||||

.fnt1 {fill:#000000;

|

||||

@@ -19,10 +19,6 @@ width="456" height="931" viewBox="-108 -20 456.0 931.0" version="1.1">

|

||||

]]>

|

||||

</style>

|

||||

<defs>

|

||||

<marker id="clock" markerWidth="8.0" markerHeight="15.0" viewBox="0 0 8.0 15.0" refX="0.5" refY="7.5" orient="auto" markerUnits="userSpaceOnUse">

|

||||

<g transform="translate(0.5,7.5)"><path d="M 0 -7 L 0 7 L 7 0 z" stroke="#000000" fill="#FFFFFF" stroke-width="1"/>

|

||||

</g>

|

||||

</marker>

|

||||

<marker id="arrow_fwd" markerWidth="8.0" markerHeight="8.0" viewBox="0 0 8.0 8.0" refX="3.2" refY="4.0" orient="auto" markerUnits="userSpaceOnUse">

|

||||

<g transform="translate(-0.0,4.0)"><path d="M 0 -4 C 2 -1, 2 1, 0 4 L 8 0 z" stroke="none" fill="#000000"/>

|

||||

</g>

|

||||

@@ -35,9 +31,13 @@ width="456" height="931" viewBox="-108 -20 456.0 931.0" version="1.1">

|

||||

<g transform="translate(3.5,3.5)"><ellipse cx="0.0" cy="0.0" rx="3.0" ry="3.0" stroke="#000000" fill="#FFFFFF" stroke-width="1"/>

|

||||

</g>

|

||||

</marker>

|

||||

<marker id="clock" markerWidth="8.0" markerHeight="15.0" viewBox="0 0 8.0 15.0" refX="0.5" refY="7.5" orient="auto" markerUnits="userSpaceOnUse">

|

||||

<g transform="translate(0.5,7.5)"><path d="M 0 -7 L 0 7 L 7 0 z" stroke="#000000" fill="#FFFFFF" stroke-width="1"/>

|

||||

</g>

|

||||

</marker>

|

||||

</defs>

|

||||

<rect x="-108" y="-20" width="100%" height="100%" fill="white"/><g transform="translate(0,0)">

|

||||

<rect x="0" y="-15.0" width="240" height="310.0" stroke="#646464" fill="#C8C8C8" stroke-width="1"/>

|

||||

<rect x="0" y="-15.0" width="280" height="310.0" stroke="#646464" fill="#C8C8C8" stroke-width="1"/>

|

||||

<g transform="translate(0,0)">

|

||||

<line x1="-20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="1"/>

|

||||

<text class="fnt1" x="10" y="0" text-anchor="normal" dy="3.5">LITEDRAM_BASE_ADDRESS</text>

|

||||

@@ -99,10 +99,10 @@ width="456" height="931" viewBox="-108 -20 456.0 931.0" version="1.1">

|

||||

<text class="fnt1" x="10" y="0" text-anchor="normal" dy="3.5">COMPLETE_PULSE_WIDTH</text>

|

||||

</g>

|

||||

</g>

|

||||

<rect x="1.0" y="-14.0" width="238.0" height="308.0" stroke="#646464" fill="none" stroke-width="3"/>

|

||||

<rect x="1.0" y="-14.0" width="278.0" height="308.0" stroke="#646464" fill="none" stroke-width="3"/>

|

||||

<g transform="translate(0,318.0)">

|

||||

<rect x="0" y="-15.0" width="240" height="67.0" stroke="#000000" fill="#C5DBFC" stroke-width="1"/>

|

||||

<text class="fnt2" x="120.0" y="0" text-anchor="middle" dy="2.5">Global control</text>

|

||||

<rect x="0" y="-15.0" width="280" height="67.0" stroke="#000000" fill="#C5DBFC" stroke-width="1"/>

|

||||

<text class="fnt2" x="140.0" y="0" text-anchor="middle" dy="2.5">Global control</text>

|

||||

<g transform="translate(0,17)">

|

||||

<line x1="-20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="1" marker-end="url(#clock)"/>

|

||||

<text class="fnt1" x="10" y="0" text-anchor="normal" dy="3.5">clk_i</text>

|

||||

@@ -115,22 +115,22 @@ width="456" height="931" viewBox="-108 -20 456.0 931.0" version="1.1">

|

||||

</g>

|

||||

</g>

|

||||

<g transform="translate(0,385.0)">

|

||||

<rect x="0" y="-15.0" width="240" height="47.0" stroke="#000000" fill="#E7FDBA" stroke-width="1"/>

|

||||

<text class="fnt2" x="120.0" y="0" text-anchor="middle" dy="2.5">UART</text>

|

||||

<rect x="0" y="-15.0" width="280" height="47.0" stroke="#000000" fill="#E7FDBA" stroke-width="1"/>

|

||||

<text class="fnt2" x="140.0" y="0" text-anchor="middle" dy="2.5">UART</text>

|

||||

<g transform="translate(0,17)">

|

||||

<line x1="-20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="1"/>

|

||||

<text class="fnt1" x="10" y="0" text-anchor="normal" dy="3.5">uart_rxd_i</text>

|

||||

<text class="fnt1" x="-30" y="0" text-anchor="end" dy="3.5" style="fill:#969696">wire</text>

|

||||

</g>

|

||||

<g transform="translate(240,17)">

|

||||

<g transform="translate(280,17)">

|

||||

<line x1="20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="1"/>

|

||||

<text class="fnt1" x="-10" y="0" text-anchor="end" dy="3.5">uart_txd_o</text>

|

||||

<text class="fnt1" x="30" y="0" text-anchor="normal" dy="3.5" style="fill:#969696">wire</text>

|

||||

</g>

|

||||

</g>

|

||||

<g transform="translate(0,432.0)">

|

||||

<rect x="0" y="-15.0" width="240" height="87.0" stroke="#000000" fill="#FFAFFD" stroke-width="1"/>

|

||||

<text class="fnt2" x="120.0" y="0" text-anchor="middle" dy="2.5">LPC interface</text>

|

||||

<rect x="0" y="-15.0" width="280" height="87.0" stroke="#000000" fill="#FFAFFD" stroke-width="1"/>

|

||||

<text class="fnt2" x="140.0" y="0" text-anchor="middle" dy="2.5">LPC interface</text>

|

||||

<g transform="translate(0,17)">

|

||||

<line x1="-20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="1" marker-end="url(#clock)"/>

|

||||

<text class="fnt1" x="10" y="0" text-anchor="normal" dy="3.5">LCLK</text>

|

||||

@@ -146,39 +146,68 @@ width="456" height="931" viewBox="-108 -20 456.0 931.0" version="1.1">

|

||||

<text class="fnt1" x="10" y="0" text-anchor="normal" dy="3.5">LFRAME</text>

|

||||

<text class="fnt1" x="-30" y="0" text-anchor="end" dy="3.5" style="fill:#969696">wire</text>

|

||||

</g>

|

||||

<g transform="translate(240,17)">

|

||||

<g transform="translate(280,17)">

|

||||

<line x1="16.16" y1="4.702643708725836e-16" x2="3.84" y2="-4.702643708725836e-16" stroke="#000000" fill="none" stroke-width="3" marker-start="url(#arrow_back)" marker-end="url(#arrow_fwd)"/>

|

||||

<text class="fnt1" x="-10" y="0" text-anchor="end" dy="3.5">LAD</text>

|

||||

<text class="fnt1" x="30" y="0" text-anchor="normal" dy="3.5" style="fill:#969696">wire <tspan fill="#039BE5">[3:0]</tspan></text>

|

||||

</g>

|

||||

<g transform="translate(240,37)">

|

||||

<g transform="translate(280,37)">

|

||||

<line x1="16.16" y1="4.702643708725836e-16" x2="3.84" y2="-4.702643708725836e-16" stroke="#000000" fill="none" stroke-width="1" marker-start="url(#arrow_back)" marker-end="url(#arrow_fwd)"/>

|

||||

<text class="fnt1" x="-10" y="0" text-anchor="end" dy="3.5">SERIRQ</text>

|

||||

<text class="fnt1" x="30" y="0" text-anchor="normal" dy="3.5" style="fill:#969696">wire</text>

|

||||

</g>

|

||||

</g>

|

||||

<g transform="translate(0,519.0)">

|

||||

<rect x="0" y="-15.0" width="240" height="67.0" stroke="#000000" fill="#B9FDE9" stroke-width="1"/>

|

||||

<text class="fnt2" x="120.0" y="0" text-anchor="middle" dy="2.5">SPI interface</text>

|

||||

<rect x="0" y="-15.0" width="280" height="87.0" stroke="#000000" fill="#B9FDE9" stroke-width="1"/>

|

||||

<text class="fnt2" x="140.0" y="0" text-anchor="middle" dy="2.5">SPI interface - PC</text>

|

||||

<g transform="translate(0,17)">

|

||||

<line x1="-20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="1" marker-end="url(#clock)"/>

|

||||

<text class="fnt1" x="10" y="0" text-anchor="normal" dy="3.5">CLK</text>

|

||||

<text class="fnt1" x="-30" y="0" text-anchor="end" dy="3.5" style="fill:#969696">wire</text>

|

||||

</g>

|

||||

<g transform="translate(0,37)">

|

||||

<line x1="-20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="1"/>

|

||||

<text class="fnt1" x="10" y="0" text-anchor="normal" dy="3.5">MOSI</text>

|

||||

<text class="fnt1" x="-30" y="0" text-anchor="end" dy="3.5" style="fill:#969696">wire</text>

|

||||

</g>

|

||||

<g transform="translate(0,57)">

|

||||

<line x1="-20" y1="0" x2="-3.5" y2="0.0" stroke="#000000" fill="none" stroke-width="1" marker-end="url(#bubble)"/>

|

||||

<text class="fnt1" x="10" y="0" text-anchor="normal" dy="3.5">CS_N</text>

|

||||

<text class="fnt1" x="-30" y="0" text-anchor="end" dy="3.5" style="fill:#969696">wire</text>

|

||||

</g>

|

||||

<g transform="translate(280,17)">

|

||||

<line x1="20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="1"/>

|

||||

<text class="fnt1" x="-10" y="0" text-anchor="end" dy="3.5">MISO</text>

|

||||

<text class="fnt1" x="30" y="0" text-anchor="normal" dy="3.5" style="fill:#969696">wire</text>

|

||||

</g>

|

||||

<g transform="translate(280,37)">

|

||||

<line x1="20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="1"/>

|

||||

<text class="fnt1" x="-10" y="0" text-anchor="end" dy="3.5">PIRQ</text>

|

||||

<text class="fnt1" x="30" y="0" text-anchor="normal" dy="3.5" style="fill:#969696">wire</text>

|

||||

</g>

|

||||

</g>

|

||||

<g transform="translate(0,606.0)">

|

||||

<rect x="0" y="-15.0" width="280" height="67.0" stroke="#000000" fill="#FBDCC4" stroke-width="1"/>

|

||||

<text class="fnt2" x="140.0" y="0" text-anchor="middle" dy="2.5">SPI interface - flash</text>

|

||||

<g transform="translate(0,17)">

|

||||

<line x1="-20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="1"/>

|

||||

<text class="fnt1" x="10" y="0" text-anchor="normal" dy="3.5">spi_dat_i</text>

|

||||

<text class="fnt1" x="-30" y="0" text-anchor="end" dy="3.5" style="fill:#969696">wire</text>

|

||||

</g>

|

||||

<g transform="translate(240,17)">

|

||||

<g transform="translate(280,17)">

|

||||

<line x1="20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="1"/>

|

||||

<text class="fnt1" x="-10" y="0" text-anchor="end" dy="3.5">spi_dat_o</text>

|

||||

<text class="fnt1" x="30" y="0" text-anchor="normal" dy="3.5" style="fill:#969696">wire</text>

|

||||

</g>

|

||||

<g transform="translate(240,37)">

|

||||

<g transform="translate(280,37)">

|

||||

<line x1="20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="1"/>

|

||||

<text class="fnt1" x="-10" y="0" text-anchor="end" dy="3.5">spi_flash_cs_o</text>

|

||||

<text class="fnt1" x="30" y="0" text-anchor="normal" dy="3.5" style="fill:#969696">wire</text>

|

||||

</g>

|

||||

</g>

|

||||

<g transform="translate(0,586.0)">

|

||||

<rect x="0" y="-15.0" width="240" height="247.0" stroke="#000000" fill="#FBDCC4" stroke-width="1"/>

|

||||

<text class="fnt2" x="120.0" y="0" text-anchor="middle" dy="2.5">DDR3 interface</text>

|

||||

<g transform="translate(0,673.0)">

|

||||

<rect x="0" y="-15.0" width="280" height="247.0" stroke="#000000" fill="#D3CBFE" stroke-width="1"/>

|

||||

<text class="fnt2" x="140.0" y="0" text-anchor="middle" dy="2.5">DDR3 interface</text>

|

||||

<g transform="translate(0,17)">

|

||||

<line x1="-20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="3"/>

|

||||

<text class="fnt1" x="10" y="0" text-anchor="normal" dy="3.5">ddram_dq</text>

|

||||

@@ -189,80 +218,80 @@ width="456" height="931" viewBox="-108 -20 456.0 931.0" version="1.1">

|

||||

<text class="fnt1" x="10" y="0" text-anchor="normal" dy="3.5">ddram_dqs_p</text>

|

||||

<text class="fnt1" x="-30" y="0" text-anchor="end" dy="3.5" style="fill:#969696">wire <tspan fill="#039BE5">[1:0]</tspan></text>

|

||||

</g>

|

||||

<g transform="translate(240,17)">

|

||||

<g transform="translate(280,17)">

|

||||

<line x1="20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="3"/>

|

||||

<text class="fnt1" x="-10" y="0" text-anchor="end" dy="3.5">ddram_a</text>

|

||||

<text class="fnt1" x="30" y="0" text-anchor="normal" dy="3.5" style="fill:#969696">wire <tspan fill="#039BE5">[15:0]</tspan></text>

|

||||

</g>

|

||||

<g transform="translate(240,37)">

|

||||

<g transform="translate(280,37)">

|

||||

<line x1="20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="3"/>

|

||||

<text class="fnt1" x="-10" y="0" text-anchor="end" dy="3.5">ddram_ba</text>

|

||||

<text class="fnt1" x="30" y="0" text-anchor="normal" dy="3.5" style="fill:#969696">wire <tspan fill="#039BE5">[2:0]</tspan></text>

|

||||

</g>

|

||||

<g transform="translate(240,57)">

|

||||

<g transform="translate(280,57)">

|

||||

<line x1="20" y1="0" x2="3.5" y2="-4.286263797015736e-16" stroke="#000000" fill="none" stroke-width="1" marker-end="url(#bubble)"/>

|

||||

<text class="fnt1" x="-10" y="0" text-anchor="end" dy="3.5">ddram_ras_n</text>

|

||||

<text class="fnt1" x="30" y="0" text-anchor="normal" dy="3.5" style="fill:#969696">wire</text>

|

||||

</g>

|

||||

<g transform="translate(240,77)">

|

||||

<g transform="translate(280,77)">

|

||||

<line x1="20" y1="0" x2="3.5" y2="-4.286263797015736e-16" stroke="#000000" fill="none" stroke-width="1" marker-end="url(#bubble)"/>

|

||||

<text class="fnt1" x="-10" y="0" text-anchor="end" dy="3.5">ddram_cas_n</text>

|

||||

<text class="fnt1" x="30" y="0" text-anchor="normal" dy="3.5" style="fill:#969696">wire</text>

|

||||

</g>

|

||||

<g transform="translate(240,97)">

|

||||

<g transform="translate(280,97)">

|

||||

<line x1="20" y1="0" x2="3.5" y2="-4.286263797015736e-16" stroke="#000000" fill="none" stroke-width="1" marker-end="url(#bubble)"/>

|

||||

<text class="fnt1" x="-10" y="0" text-anchor="end" dy="3.5">ddram_we_n</text>

|

||||

<text class="fnt1" x="30" y="0" text-anchor="normal" dy="3.5" style="fill:#969696">wire</text>

|

||||

</g>

|

||||

<g transform="translate(240,117)">

|

||||

<g transform="translate(280,117)">

|

||||

<line x1="20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="3"/>

|

||||

<text class="fnt1" x="-10" y="0" text-anchor="end" dy="3.5">ddram_dm</text>

|

||||

<text class="fnt1" x="30" y="0" text-anchor="normal" dy="3.5" style="fill:#969696">wire <tspan fill="#039BE5">[1:0]</tspan></text>

|

||||

</g>

|

||||

<g transform="translate(240,137)">

|

||||

<g transform="translate(280,137)">

|

||||

<line x1="20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="1"/>

|

||||

<text class="fnt1" x="-10" y="0" text-anchor="end" dy="3.5">ddram_clk_p</text>

|

||||

<text class="fnt1" x="30" y="0" text-anchor="normal" dy="3.5" style="fill:#969696">wire</text>

|

||||

</g>

|

||||

<g transform="translate(240,157)">

|

||||

<g transform="translate(280,157)">

|

||||

<line x1="20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="1"/>

|

||||

<text class="fnt1" x="-10" y="0" text-anchor="end" dy="3.5">ddram_cke</text>

|

||||

<text class="fnt1" x="30" y="0" text-anchor="normal" dy="3.5" style="fill:#969696">wire</text>

|

||||

</g>

|

||||

<g transform="translate(240,177)">

|

||||

<g transform="translate(280,177)">

|

||||

<line x1="20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="1"/>

|

||||

<text class="fnt1" x="-10" y="0" text-anchor="end" dy="3.5">ddram_odt</text>

|

||||

<text class="fnt1" x="30" y="0" text-anchor="normal" dy="3.5" style="fill:#969696">wire</text>

|

||||

</g>

|

||||

<g transform="translate(240,197)">

|

||||

<g transform="translate(280,197)">

|

||||

<line x1="20" y1="0" x2="3.5" y2="-4.286263797015736e-16" stroke="#000000" fill="none" stroke-width="1" marker-end="url(#bubble)"/>

|

||||

<text class="fnt1" x="-10" y="0" text-anchor="end" dy="3.5">ddram_cs_n</text>

|

||||

<text class="fnt1" x="30" y="0" text-anchor="normal" dy="3.5" style="fill:#969696">wire</text>

|

||||

</g>

|

||||

<g transform="translate(240,217)">

|

||||

<g transform="translate(280,217)">

|

||||

<line x1="20" y1="0" x2="3.5" y2="-4.286263797015736e-16" stroke="#000000" fill="none" stroke-width="1" marker-end="url(#bubble)"/>

|

||||

<text class="fnt1" x="-10" y="0" text-anchor="end" dy="3.5">ddram_reset_n</text>

|

||||

<text class="fnt1" x="30" y="0" text-anchor="normal" dy="3.5" style="fill:#969696">wire</text>

|

||||

</g>

|

||||

</g>

|

||||

<g transform="translate(0,833.0)">

|

||||

<rect x="0" y="-15.0" width="240" height="87.0" stroke="#000000" fill="#D3CBFE" stroke-width="1"/>

|

||||

<text class="fnt2" x="120.0" y="0" text-anchor="middle" dy="2.5">Misc</text>

|

||||

<g transform="translate(240,17)">

|

||||

<g transform="translate(0,920.0)">

|

||||

<rect x="0" y="-15.0" width="280" height="87.0" stroke="#000000" fill="#D3FECB" stroke-width="1"/>

|

||||

<text class="fnt2" x="140.0" y="0" text-anchor="middle" dy="2.5">Misc</text>

|

||||

<g transform="translate(280,17)">

|

||||

<line x1="20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="1"/>

|

||||

<text class="fnt1" x="-10" y="0" text-anchor="end" dy="3.5">led_r</text>

|

||||

<text class="fnt1" x="30" y="0" text-anchor="normal" dy="3.5" style="fill:#969696">wire</text>

|

||||

</g>

|

||||

<g transform="translate(240,37)">

|

||||

<g transform="translate(280,37)">

|

||||

<line x1="20" y1="0" x2="0" y2="0" stroke="#000000" fill="none" stroke-width="1"/>

|

||||

<text class="fnt1" x="-10" y="0" text-anchor="end" dy="3.5">led_g</text>

|

||||

<text class="fnt1" x="30" y="0" text-anchor="normal" dy="3.5" style="fill:#969696">wire</text>

|

||||

</g>

|

||||

<g transform="translate(240,57)">

|

||||

<g transform="translate(280,57)">

|

||||

<line x1="20" y1="0" x2="3.5" y2="-4.286263797015736e-16" stroke="#000000" fill="none" stroke-width="1" marker-end="url(#bubble)"/>

|

||||

<text class="fnt1" x="-10" y="0" text-anchor="end" dy="3.5">led_b</text>

|

||||

<text class="fnt1" x="30" y="0" text-anchor="normal" dy="3.5" style="fill:#969696">wire</text>

|

||||

</g>

|

||||

</g>

|

||||

<rect x="1.0" y="304.0" width="238.0" height="600.0" stroke="#000000" fill="none" stroke-width="3"/>

|

||||

<rect x="1.0" y="304.0" width="278.0" height="687.0" stroke="#000000" fill="none" stroke-width="3"/>

|

||||

</svg>

|

||||

|

||||

|

Before Width: | Height: | Size: 15 KiB After Width: | Height: | Size: 17 KiB |

@@ -133,7 +133,7 @@ Milestones:

|

||||

- implementation of TPM register space

|

||||

- review and update existing documentation, add entry to changelog

|

||||

|

||||

State: Backlog

|

||||

State: [Done](../changelog/#2024-03-14)

|

||||

|

||||

## 8. Explore the usage of using simpler hardware platform

|

||||

|

||||

@@ -168,7 +168,7 @@ Milestones:

|

||||

- test suite: use in real-world scenario (Fobnail)

|

||||

- review and update existing documentation, add entry to changelog

|

||||

|

||||

State: Backlog

|

||||

State: In progress

|

||||

|

||||

## 10. Unique identification and randomness source

|

||||

|

||||

@@ -186,7 +186,7 @@ Milestones:

|

||||

- test suite: Windows HLK

|

||||

- review and update existing documentation, add entry to changelog

|

||||

|

||||

State: Backlog

|

||||

State: In progress

|

||||

|

||||

## 11. Manufacturing process

|

||||

|

||||

@@ -218,4 +218,4 @@ Milestones:

|

||||

- prepare configuration file for whole project

|

||||

- review and update existing documentation, add entry to changelog

|

||||

|

||||

State: Backlog

|

||||

State: In progress

|

||||

|

||||

File diff suppressed because one or more lines are too long

@@ -0,0 +1,3 @@

|

||||

SPDX-FileCopyrightText: 2024 3mdeb <contact@3mdeb.com>

|

||||

|

||||

SPDX-License-Identifier: CC-BY-SA-4.0

|

||||

@@ -21,7 +21,7 @@ not take responsibility for potential damage caused by it. You have been warned.

|

||||

## Pinout for TwPM based on OrangeCrab

|

||||

|

||||

This is valid for TwPM built for [OrangeCrab](https://github.com/orangecrab-fpga/orangecrab-hardware)

|

||||

from release v0.2.0.

|

||||

from release v0.3.0.

|

||||

|

||||

Pinout from [official documentation](https://orangecrab-fpga.github.io/orangecrab-hardware/docs/pinout/):

|

||||

|

||||

@@ -34,6 +34,20 @@ as they are described in .lpf files, this is what FPGA tools need) and I/O

|

||||

numbers (i.e. what is printed on the board, you will most likely use this to

|

||||

find the correct pin).

|

||||

|

||||

In addition to signals for exchanging data with the mainboard, `3V3` and `GND`

|

||||

must also be connected to supply power to the OrangeCrab.

|

||||

|

||||

If those pins need to be changed for any reason, it can be done in

|

||||

[orangecrab.lpf file](https://github.com/Dasharo/TwPM_toplevel/blob/main/fpga/orangecrab.lpf).

|

||||

Remember to change `SITE` of given signal to another physical pin, not only the

|

||||

comment which contains I/O number. For OrangeCrab, mapping between I/O pins and

|

||||

physical ports can be read from [schematics](https://github.com/orangecrab-fpga/orangecrab-hardware/blob/main/hardware/orangecrab_r0.2.1/plot/OrangeCrab.pdf).

|

||||

|

||||

Note that only one of the below interfaces is enabled at any given time.

|

||||

Switching between them requires rebuilding and flashing the new bitstream.

|

||||

|

||||

### LPC

|

||||

|

||||

| Signal name | Physical Pin | I/O number |

|

||||

|-------------|:------------:|:----------:|

|

||||

| LCLK | H2 | 12 |

|

||||

@@ -45,14 +59,15 @@ find the correct pin).

|

||||

| LAD[3] | B10 | 5 |

|

||||

| SERIRQ | C9 | SCL |

|

||||

|

||||

In addition to those signals, `3V3` and `GND` must also be connected to supply

|

||||

power to the OrangeCrab.

|

||||

### SPI

|

||||

|

||||

If those pins need to be changed for any reason, it can be done in

|

||||

[orangecrab.lpf file](https://github.com/Dasharo/TwPM_toplevel/blob/main/fpga/orangecrab.lpf).

|

||||

Remember to change `SITE` of given signal to another physical pin, not only the

|

||||

comment which contains I/O number. For OrangeCrab, mapping between I/O pins and

|

||||

physical ports can be read from [schematics](https://github.com/orangecrab-fpga/orangecrab-hardware/blob/main/hardware/orangecrab_r0.2.1/plot/OrangeCrab.pdf).

|

||||

| Signal name | Physical Pin | I/O number |

|

||||

|-------------|:------------:|:----------:|

|

||||

| CLK | H2 | 12 |

|

||||

| MISO | J2 | 13 |

|

||||

| MOSI | A8 | 11 |

|

||||

| CS_N | B8 | 10 |

|

||||

| PIRQ | C9 | SCL |

|

||||

|

||||

## Mainboard pinouts

|

||||

|

||||

@@ -60,10 +75,10 @@ The presented list has only mainboards that are confirmed to be valid. You are

|

||||

free to try it on the boards not listed below, assuming [you know what you're

|

||||

doing](#warning).

|

||||

|

||||

### Protectli VP46xx

|

||||

### Protectli VP46xx (LPC)

|

||||

|

||||

Protectli platforms from [VP46xx series](https://eu.protectli.com/vault-6-port/)

|

||||

have header compatible with [TPM-01](https://kb.protectli.com/kb/tpm-on-the-vault/#articleTOC_1).

|

||||

have header compatible with [TPM-01](https://eu.protectli.com/product/tpm-module/).

|

||||

It is 2x10 pin header, with key on pin 4. It is dangerously similar to multiple

|

||||

Gigabyte and Supermicro TPMs, but their layout is different so those are not

|

||||

compatible.

|

||||

@@ -89,3 +104,30 @@ Pinout:

|

||||

|

||||

Some of the `NC` pins are actually used for other purposes. For clarity and to

|

||||

avoid making mistakes they are not marked above.

|

||||

|

||||

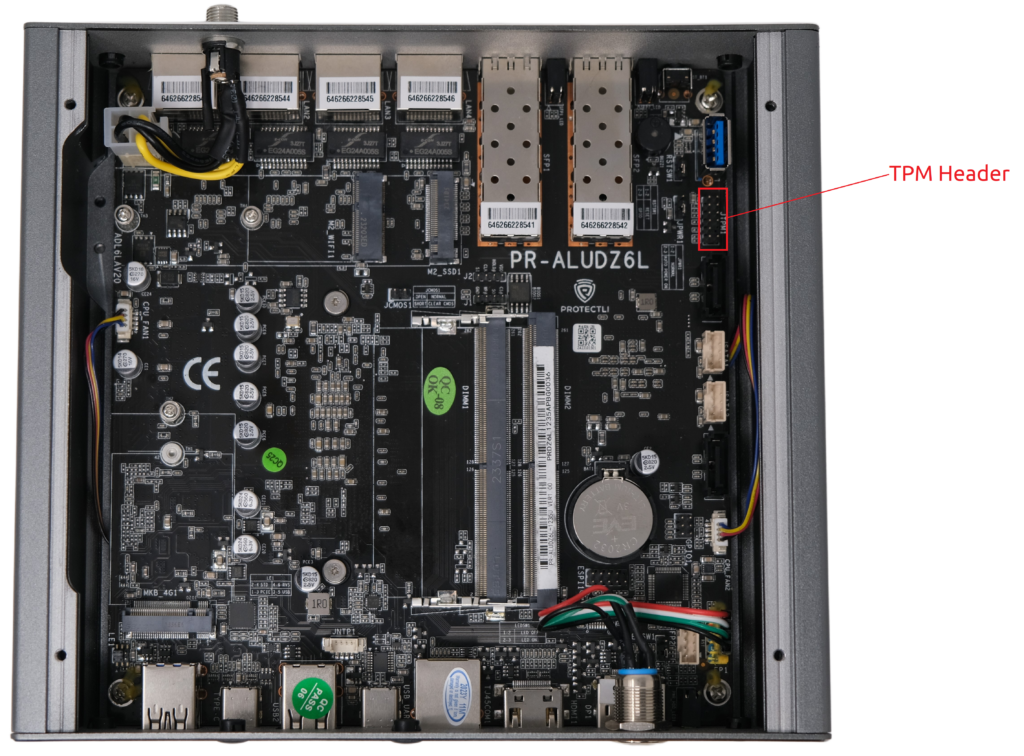

### Protectli VP66xx (SPI)

|

||||

|

||||

Protectli platforms from [VP66xx series](https://eu.protectli.com/vault-6-port/)

|

||||

have header compatible with [TPM-02](https://eu.protectli.com/product/tpm02/).

|

||||

It is 2x6 pin header, with key on pin 10, and a pitch different than OrangeCrab

|

||||

(2.00 mm instead of 2.54 mm), make sure you have proper wiring. The header is

|

||||

the same as on some of the MSI boards. Gigabyte uses rotated version of this

|

||||

pinout, while it looks the same, the pinout is different.

|

||||

|

||||

|

||||

|

||||

Pinout:

|

||||

|

||||

{ align=left }

|

||||

|

||||

| Pin No. | Definition | Pin No. | Definition |

|

||||

|:-------:|------------|:-------:|------------|

|

||||

| 1 | VDD (3.3V) | 2 | CS_N |

|

||||

| 3 | MISO | 4 | MOSI |

|

||||

| 5 | NC | 6 | CLK |

|

||||

| 7 | GND | 8 | NC |

|

||||

| 9 | NC | 10 | key |

|

||||

| 11 | NC | 12 | PIRQ |

|

||||

|

||||

Some of the `NC` pins are actually used for other purposes. For clarity and to

|

||||

avoid making mistakes they are not marked above.

|

||||

|

||||

Reference in New Issue

Block a user